057

04.01.2020, 10:56 Uhr

holm

|

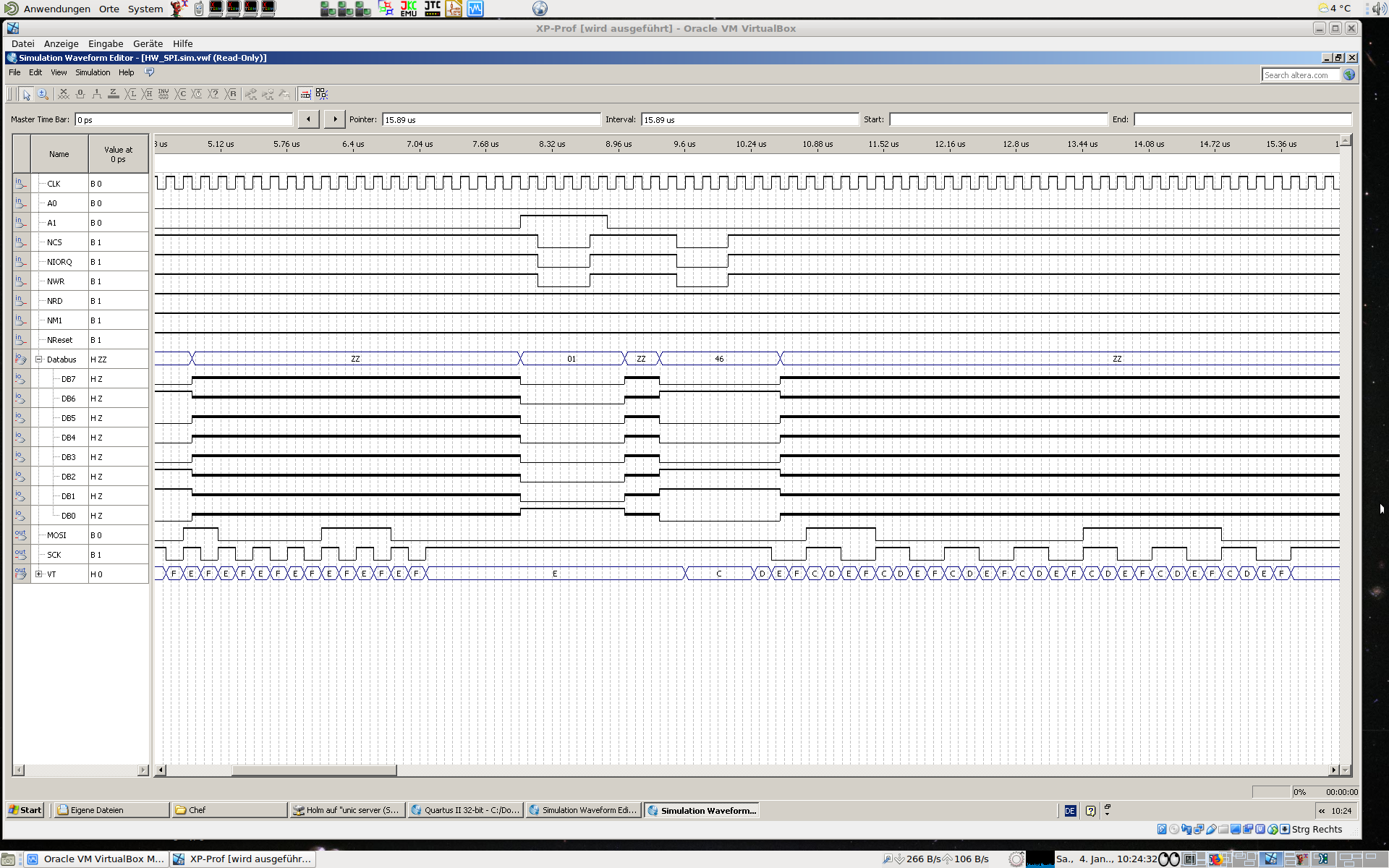

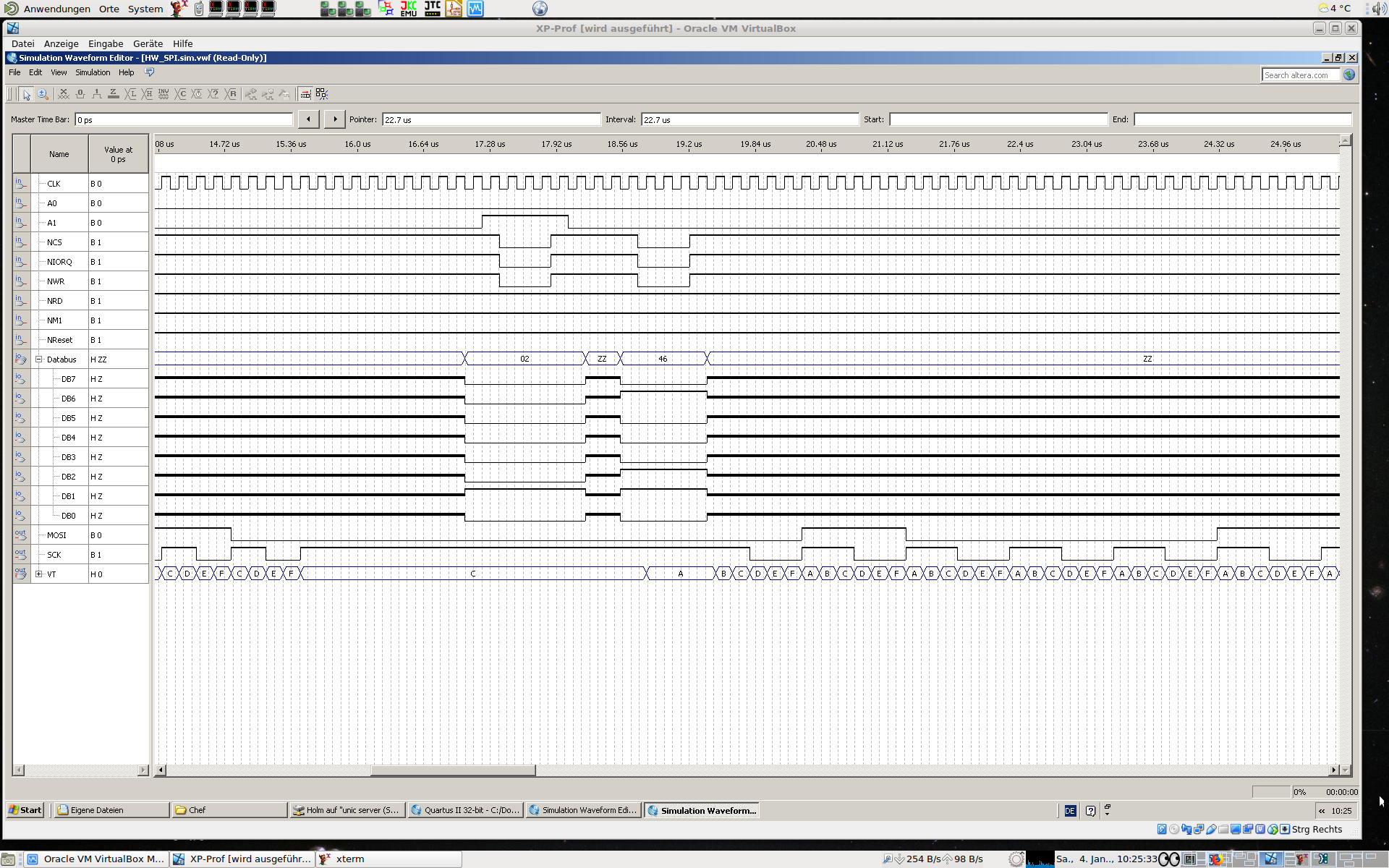

..Du bist ja so gemein. Die Simu hing nicht dran, weil das mittlerweile eine längliche Tapete ist, ich habe mehrere Teilerfaktoren nacheinander ausprobiert und auch das rückgelesene Byte wieder abgeholt.

Ich habe alle Teilerfaktoren zwischen 000 und 111 getestet, funktioniert so.

Zum asynchron gesetzten dff am Ausgang, ja, das stört mich auch noch, evtl. versuche ichs da mit einem getakteten JK FF noch einmal. Ich habe mal nach meinem Vorrat von EPM3064 geschaut, der beschränkt sich auf 2 Stück, genauso wie EPM3032. Ich habe allerdings eine größere Anzahl EPM7064ALC44-12 da,

also Serie MAX7000 ..und die wird wieder von Quartus nicht unterstützt, muß mal sehen ob die nachgerüstet werden kann...

Unterstützt wird MAX7000 allerdings von Altera MAX2Plus..was sich auch noch auf meinem Rechner herumtreibt, freilich sind die Schaltungseditoren nicht kompatibel zwischen den beiden Paketen, auch wenn ich vermute das das konvertierbar ist, ich muß da nochmal suchen. Da die Schaltung mittlerweile ausreichend vergriesgnaddelt ist, habe ich sie mit max2plus gestern nochmal (um-) gezeichnet, logischer aufgebaut, kommt nachher noch. Freundlicherweise kann mein Labtool48 mit Dataman48 Software auch den MAX7000, ich habe da auch noch EPM7160 in PLCC84 und solches Zeuch...

MAX7000 hat eine Besonderheit, Tristate geht da an einem Ausgang nur, wenn ein externe Pin die Tristate Umschaltung macht, hab komisch geguckt als der Compiler sagte ich soll extern 2x 2Pins miteinander verbinden. auf diese Weise wird von der internen Logik mit einem Ausgang ein anderer Ausgang in Tritate gesteuert :-O

Egal, billige und schnelle 5V Bausteine!

MAX3000 und MAX7000S sind aufwärtskompatibel, man kann die 3000er Daten direkt in einen 7000s brennen.

Zum Decoder/Multiplexer:

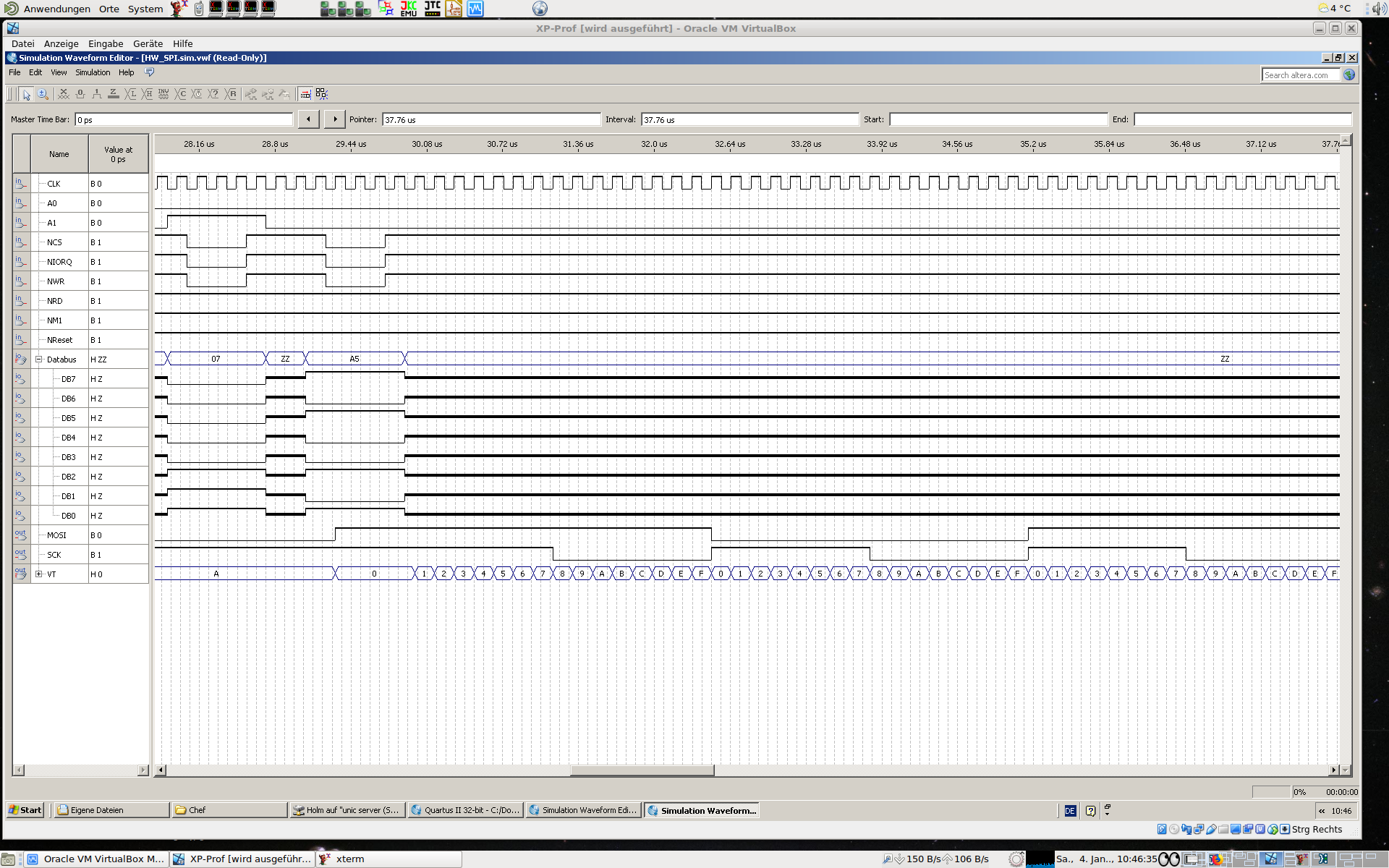

Wie Du an der Simu sehen kannst funktioniert das, bei jedem Teilerverhältnis. Ich hatte schon irgendwann weiter oben festgestellt das mich ungerade Teielerverhältnisse nicht unbedingt interessieren, das läßt sich auch so fein genug einstellen. Genauso ist die Frage ob das SCK Signal exakt 50% Tastverhältnis hat, eher irrelevant, ich wollte aber eben keine schmalen Nadeln die 6Mhz entsprechen.

Das was nun da rauskommt ist besser als worksforme.

Der 74138 war ursprünglich ein 74154..bis ich gemerkt habe das die unter Hälfte der Ausgänge unbelegt ist. Ist ja auch logisch. Für das aktiv schalten von SCK sind die Zählerstände des 161 unterhalb 8 uninteressant, deswegen fällt der untere Decoderteil weg, das ist also die von Dir vermißte Division durch 2.

Der auf den Zählerstand "F" folgende Takt setzt SCK wieder auf inaktiv. Das ist schon die ganze Zauberei.

Der Multiplexer wird durch den vorgeladenen Teilerfaktor (ok die Negation davon, aber das beeinflußt nur die Reihenfolge der Eingänge) gesteuert. Es gibt für jedesTeilerverhältnis einen aktiven Eingang. Der Decoder zeigt die Zählerstände des 161 an und eine Verbindung eines Ausgang zum aktiven MUX Eingang spezifiziert den Takt an dem SCK eingeschaltet wird. Abgeschaltet wird immer ein Takt nach "F".

Vorteiler 7, Daten A5 statt 46!

Ich habe Tagelang die Software auf meinen Server geladen ..mit dem Ziel das Du selber simulieren kannst!

Gruß,

Holm

--

float R,y=1.5,x,r,A,P,B;int u,h=80,n=80,s;main(c,v)int c;char **v;

{s=(c>1?(h=atoi(v[1])):h)*h/2;for(R=6./h;s%h||(y-=R,x=-2),s;4<(P=B*B)+

(r=A*A)|++u==n&&putchar(*(((--s%h)?(u<n?--u%6:6):7)+"World! \n"))&&

(A=B=P=u=r=0,x+=R/2))A=B*2*A+y,B=P+x-r;}

Dieser Beitrag wurde am 04.01.2020 um 11:13 Uhr von holm editiert. |